# A two-stage opamp frequency Compensation technique by splitting the 2<sup>nd</sup> stage

R. Nagulapalli, K. Hayatleh, S Barker <a href="mailto:khayatleh@brookes.ac.uk">khayatleh@brookes.ac.uk</a>

Brookes University, oxford, UK.

Abstract—In this paper miller compensation of opamp has been explained intuitively and discussed the problems existing with this traditional way. Proposed an area/power efficient technique by splitting the second stage has been proposed. The splitting introduces an extra zero in the transfer function such that it will improve the stability. This tech was implemented in 45nm CMOS technology and simulated with Spectre. Simulation results show that the proposed circuit saves 50% of the capacitance area compared to the miller technique. The circuit draws 320uA current from 1.5V supply and occupying 0.003108mm2 silicon area.

Keywords—Opamp, Miller, capacitor, Pole, Bandwidth, phase margin, noise.

### I. INTRODUCTION

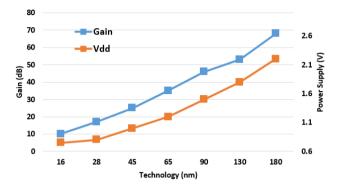

The present electronic systems greatly depend on the performance of the amplifier. Both high gain and high bandwidth while consuming very low power are the primary design goal. With the ever-decreasing size of transistors due to technology scaling, the internal electric field of the junctions has been increased greatly which creates all short channel second-order effects like Drain induced barrier lower (DIBL), channel length modulation etc [1]. To combat the second order effects devices researchers have been forced to decreased decreasing the supply voltage, thus the voltage gain and output swing of the amplifiers are greatly decreased. Fig. 1 shows how the voltage gain of a single stage amplifier decreases with the technology, due to velocity situation and channel length modulation, the gain has been decreased by less than 10 around 28nm technology. Another difficulty with the scaling is exponential increase in the leakage current through the gate and drain to substrate junction leakage. Gate leakage current is strongly depending on the thickness of the Sio<sub>2</sub> oxide and this has been decreasing with technology scaling and currently, it is in the order of few nm in 65nm [2]. To reduce the leakage while keeping the oxide thickness same as proposed, threshold voltage (Vth) has been kept or decreased with much lesser pace compared to the supply voltage (V<sub>dd</sub>). Fig. 1 also shows how the V<sub>dd</sub> is decreasing with the technology. But unfortunately, higher V<sub>th</sub> for a given V<sub>dd</sub> reduces the signal swing for a given power dissipation. Generally, sensor or bio-medical application requires 80dB to keep the settling error less than 0.1%.

Fig. 1. Gain vs Technology Node

Conventional telescopic or folded Cascode amplifiers, which increases the gain by stacking up transistors is a good technique to increase the gain but at the cost of increased power supply voltage. Or for a given supply the output swing is getting decreased. Often multistage amplifier is a widely used technique to enhance the voltage gain by cascading the number of gain stages horizontally. In this way, circuits can compatible with the low voltage technologies and give acceptable voltage gain. For example, two-stage operation amplifier is very popular in both industry and academia, which achieves very high gain as well acceptable output swing by using a Common Source amplifier as a final stage. This popularity is because of its un-conditionally stable nature irrespective of the feedback factor and load capacitance, hence it can be used as general purpose opamp [2]. However, multistage amplifiers are needed to get higher gain even though the voltage gain is decreasing with technology scaling. Each stage contributes one lowfrequency pole in the overall transfer function hence several low-frequency poles in the multi stage combination will leads to un-stable amplifier in the closed-loop configuration. Usually, instability gives peaking in the frequency response and ringing in the time domain and compromises the performance. Often frequency compensation is essential for stable operation, which consumes higher power and silicon area to place the compensation capacitor [3]. This motivates to find an area and power efficient compensation technique.

The rest of the paper has been organized as follows. Section II reviews the existing miller compensation intuitively and design guidelines, Section III explains the proposed technique qualitatively as well quantitatively and section IV summarizes the prototype results.

## II. REVIEW OF MILLER COMPENSATION.

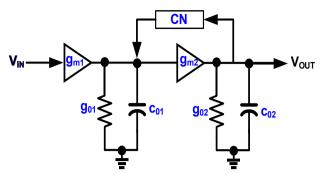

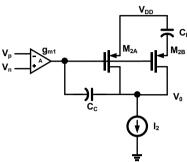

Fig. 2. Conventional Miller Compensation Model

Fig. 3. Conventional Compensation-Network (CN) circuits

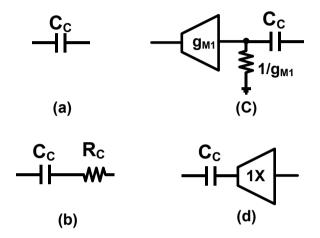

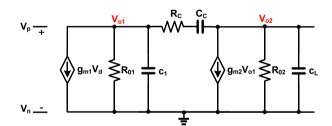

shows the conventional two-stage miller compensation, where the first stage is a typical single stage opamp with the high impedance active load, whereas common source as the second stage. A compensation network (CN) consists of resistor and capacitor will be generally added to compensate the system for improved stability. There have been four types of the CN's as shown in fig. 3. (a) shows Simple miller compensation (SMC) with a simple capacitor as CN, (b) shows SMC with a Zero nulling resistor whose value equal to  $\frac{1}{gm_2}$  , (c) shows SMC with a current buffer to push RHP to very high frequency and (d) shows SMC with a voltage buffer. Without any compensation network opamp dominate pole at  $\frac{1}{R_{01}C_{01}}$  and non-dominate pole at  $\frac{1}{R_{02}C_{02}}$ . Fig. 4 depicts the small signal model of the miller compensation. The compensated (means capacitor as a feedback element) the opamp transfer function can be written as

$$\frac{V_{out}}{V_{in}} = \frac{g_{m1}g_{m2}\left(1 - \frac{SCC}{g_{m2}}\right)}{AS^2 + BS + C} \tag{1}$$

Where  $A=c_{01}c_{c}+c_{01}c_{02}+c_{02}c_{c}$  $B=c_c(g_{m2}+g_{02}+g_{01})+c_{02}g_{01}+c_{01}g_{02}$  and  $C=g_{01}g_{02}$  By using wide pole separation Closed loop poles can be written as

$$P_1 = \frac{g_{01}}{c_c \left(\frac{g_{m2}}{g_{01}} + 1 + \frac{g_{01}}{g_{02}}\right) + c_{01} + c_{02} \frac{g_{01}}{g_{02}}} \tag{2}$$

$$P_{2} = \frac{g_{02} + g_{m2} \frac{C_{C}}{C_{C} + C_{01}} + g_{01} \frac{C_{C} + C_{02}}{C_{C} + C_{01}}}{C_{02} + \frac{C_{C} C_{01}}{C_{C} + C_{01}}}$$

(3)

From the above two equations it is evident that dominate pole frequency (P<sub>1</sub>) has been decreased and non-dominate pole frequency (P<sub>2</sub>) went high. For this reason, Miller compensation will also be known as pole-splitting compensation. Almost every researcher has shown the math's to show the splitting but there is no intuitive explanation why poles do so [4]. Looking at the fig.2 it is clear that miller capacitor will be multiplied by the -ve gain of the second stage hence the load capacitance seen by the first stage will be increased by  $g_{m2}*r_{02}$  times and  $P_1$  will move down. Whereas at high frequency, the impedance looking at the output of the second will increases a lot, because of the feedback formed by the  $C_C$  and  $C_{01}$ . Effective impedance has decreased and pole frequency went up. The approximate location P2 can be expressed as (4).  $P_2 = \frac{g_{m2}}{c_L} \frac{1}{1 + \frac{c_{01}}{c_C}}$

$$P_2 = \frac{g_{m2}}{c_L} \frac{1}{1 + \frac{c_{01}}{c_C}} \tag{4}$$

This indicates that the total amount of phase shift introduced by the loop has decreased by the ratio of the final pole locations. Also, this technique has increased the system bandwidth considerably compared to the dominant pole compensation because P<sub>2</sub> frequency increased [3].

Fig. 4. Small signal model of the miller technique

# III. PROPOSED COMPENSATION TECHNIQUE.

In the past, although various miller compensation schemes have been proposed to improve the gain bandwidth product, complexity also increased interims of additional amplifier stages and capacitors [3-10]. Miller compensation with a nulling resistor introduces a right half zero (RHP) which compromises the stability. Ahuja [5] and [6] proposed a current buffer in series with a compensation capacitor to cancel RHP, the downside of this technique is complex poles in the closed loop. A damping stage based compensation proposed in [3]- [5], but the technique has poor power supply rejection (PSRR). [8] has proposed cascade compensation, by connection compensation capacitor at a low impedance node to eliminate RHP zero, often creating a low impedance node with-in the Opamp demands a lot of power. The downside of existing miller technique is the excessive power consumption in the second stage because, for a given compensation capacitor,  $2^{nd}$   $g_m$  should be chosen such that second dominate pole should 2-3X higher frequency relative to the Unity Gain Bandwidth (UGB). Typically, second stage load capacitance will be decided by the preceding stage, hence the only one variable to adjust is the second stage  $g_m$ , unfortunately this will cost us significant power. [7] proposed feedforward technique to improve the stability by adding another parallel stage such that zero would be formed near UGB, this is having serious settling problems. [9] proposed a split length technique to improve the stability but at the cost of the split devices.

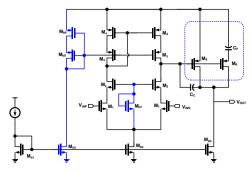

Fig. 5. Proposed compensation technique.

Fig. 6 shows the proposed concept of the compensation, basically the second stage has been split into two parts,  $M_{2A}$  transistor carries bias current for linearity requirements, whereas  $M_{2B}$  transistor capacitively coupled such that it won't draw any current. At high frequency means beyond the unity gain bandwidth of the opamp,  $C_F$  offers low impedance such that the second stage  $g_m$  is  $g_{m2A} + g_{m2B}$ , hence second stage pole has been moved to a high frequency which results in better phase margin [7]. The approximated equivalent second stage  $g_m$  frequency response can be expressed as follows.

$$G_{m-second} = g_{m2A} + \frac{g_{m2B}}{1 + \frac{g_{m2B}}{SC_F}}$$

$$= g_{m2A} \frac{{}^{1+SC_F} \left(\frac{1}{g_{m2A}} + \frac{1}{g_{m2B}}\right)}{{}^{1+\frac{SC_F}{g_{m2B}}}}$$

(5)

(5) Reveals high-frequency pole compared to the existing one, here  $g_{m2A}/g_{m2B}$  plays a significant role. Careful adjustment of the series capacitor ( $C_F$ ) with  $M_{2B}$  improves phase margin by  $24^{\circ}$ . With the traditional technique to improve phase margin by this amount second stage current needs to increase by 1.19 times, hence this technique saved 19% of the second stage current. The other important aspect of the opamp is not effected by the proposal like slew rate, input referred offset [10]. Slew rate depends mainly on the first stage bias current and compensation capacitor hence not affected by this as long  $M_{2A}$  current is higher than first stage current (which is a typical scenario).

Fig. 6. Implementation of the proposed Technique.

### IV. SIMULATION RESULTS

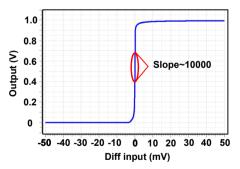

To demonstrate the efficiency of the proposed technique. it has been implemented in 8-metal and 1-poly standard 45nm CMOS technology and traditional miller compensated opamp also been implemented for comparison purpose. The targeted gain of the amplifier is 80dB in the typical process and at room temperature. It draws 320µA current from 1.5V supply voltage. The total capacitance required to composite the opamp is only 750fF, whereas the miller technique requires almost 1.6pF, which reveals that proposed technique saved 50% of the capacitance. Fig.7 shows the dc transfer characteristics of the opamp with differential input on the Xaxis and the output voltage on Y-axis. The slope around the zero-differential voltage will give a reasonable estimate of the gain, as shown in fig it is ~10000. Such a high gain is because of the cascode stage in the first stage and they have been biased in the weak-inversion region. Fig.8 shows the open-loop frequency response (magnitude as well as phase), which shows 80dB loop-gain at low frequency, 2MHz unity gain bandwidth (UGB). The Phase margin (PM) in the unity gain configuration is 500, which is sufficient to have ringing less closed-loop step response. Input referred offset is a very critical parameter for sensor application, as it compromises the sensitivity of the sensor. The typical acceptable offset is maximum of 2mV. Fig. 9 shows the simulated input referred offset, with a mean of 0mV and sigma of 0.45mV. With-in 3sigma distribution, the achieved offset is 1.35mV.

Fig. 7. Dc transfer characteristics.

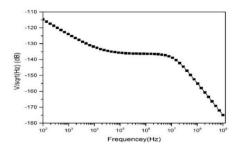

Fig. 8. Simulated input referred Noise PSD.

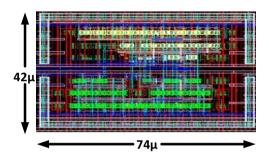

Fig. 10 shows the noise PSD of the compensated amplifier, it shows -140dB at the bandwidth and integrated noise around the frequency band is  $1.2\mu V.Fig.$  11 shows the model layout of the proposed circuit. It occupies 74um\*42um silicon area. Every transistor has been laid with proper care towards Mismatch. Special care has been taken for well proximity effect (WPE) and Shallow trench isolation (STI), by adding enough dummies for each device and keeping MOSFET away from NWELL [11].

Fig. 9. Layout of the circuit.

# V. CONCLUSION

In this paper, an area efficient opamp compensation technique has been proposed and validated with the simulation results. Demonstrated 50% saving in the capacitance area. Post layout simulations show 80dB dc gain and 2MHz bandwidth and require 750fF capacitor to achieve 50° Phase margin. Circuit occupies 0.003108mm² silicon area. Implemented in 45nm CMOS and circuit draws 320uW while powered from 1.5V Power supply.

# REFERENCES

- [1] "Overall Roadmap Technology Characteristics (ORTC)," 03/19/2009, 2009; http://www.itrs.net/Links/2005ITRS/ExecSum2005.pdf.

- [2] Nagulapalli, R., Hayatleh, K., Barker, S. et al. An OTA gain enhancement technique for low power biomedical applications. Analog Integr Circ Sig Process 95, 387–394 (2018).

- [3] R. Nagulapalli, K. Hayatleh, S. Barker, and S. Sridevi, "A Microwatt Low Voltage Bandgap Reference for Bio-medical Applications," 2017 International Conference on Recent Advances in Electronics and Communication Technology (ICRAECT), Bangalore, 2017, pp. 61-65.

- [4] A. Awny et al., "23.5 A dual 64Gbaud 10kΩ 5% THD linear differential transimpedance amplifier with automatic gain control in 0.13μm BiCMOS technology for optical fiber coherent

- receivers," 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, 2016, pp. 406-407

- [5] R. Nagulapalli, K. Hayatleh, S. Barker, S. Zourob and A. Venkatareddy, "A novel current reference in 45nm cmos technology," 2017 Second International Conference on Electrical, Computer and Communication Technologies (ICECCT), Coimbatore, 2017, pp. 1-4.

- [6] R. Nagulapalli, K. Hayatleh, S. Barker, S. Zourob and A. Venkatareddy, "A CMOS technology friendly wider bandwidth opamp frequency compensation," 2017 Second International Conference on Electrical, Computer and Communication Technologies (ICECCT), Coimbatore, 2017, pp. 1-4

- [7] R. Nagulapalli, K. Hayatleh, S. Barker, S. Zourob, N. Yassine and B. N. K. Reddy, "High Performance Circuit Techniques for Nueral Front-End Design in 65nm CMOS," 2018 9th International Conference on Computing, Communication and Networking Technologies (ICCCNT), Bangalore, 2018, pp. 1-4

- [8] A. Awny et al., "A 40 Gb/s Monolithically Integrated Linear Photonic Receiver in a \$0.25~\mu {\rm m}\$ BiCMOS SiGe:C Technology," in *IEEE Microwave and Wireless Components Letters*, vol. 25, no. 7, pp. 469-471, July 2015

- [9] R. Nagulapalli, K. Hayatleh, S. Barker, S. Zourob, N. Yassine and B. N. K. Reddy, "A Technique to Reduce the Capacitor Size in Two Stage Miller Compensated Opamp.," 2018 9th International Conference on Computing, Communication and Networking Technologies (ICCCNT), Bangalore, 2018, pp. 1-4.

- [10] R. Nagulapalli, S. Zourob, K. Hayatleh, N. Yassine, S. Barker and A. Venkatareddy, "A compact high gain opamp for Bio-medical applications in 45nm CMOStechnology," 2017 2nd IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), Bangalore, 2017, pp. 231-235

- [11] Nagulapalli, R., Hayatleh, K., Barker, S. et al. A novel high CMRR trans-impedance instrumentation amplifier for biomedical applications. Analog Integr Circ Sig Process 98, 233–241 (2019)

- [12] R. Nagulapalli, K. Hayatleh, S. Barker, S. Zourob, N. Yassine and S. Sridevi, "A PVT insensitive programmable amplifier for biomedical applications," 2017 International conference on Microelectronic Devices, Circuits and Systems (ICMDCS), Vellore, 2017, pp. 1-5.

- [13] Nagulapalli, R., Hayatleh, K.: A 0.6 V MOS-only voltage reference for biomedical applications with 40 ppm/ooC temperature drift. J. Circuits Syst. Comput. 27(8), 1850128 (2018)

- [14] B.K. Thandri, J. Silva-Martinez, "A robust feedforward compensation scheme for multistage operational transconductance amplifiers with no Miller capacitors", *IEEE Journal of Solid-State Circuits*, vol. 38, no. 2, pp. 237-243, Feb 2003.

- [15] R. Nagulapalli, K. Hayatleh, S. Barker, S. Zourob and A. Venkatreddy, "A Low Voltage Opamp Based on Current Mirror Technique for Biomedical applications," 2018 3rd IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), Bangalore, India, 2018, pp. 901-904

- [16] Nagulapalli, R., Hayatleh, K., Barker, S. et al. A CMOS blood cancer detection sensor based on frequency deviation detection. Analog Integr Circ Sig Process 92, 437–442 (2017).

- [17] R. Nagulapalli, K. Hayatleh, S. Barker, B. N. K. Reddy and B. Seetharamulu, "A Low Power Miller Compensation Technique for Two Stage Op-amp in 65nm CMOS Technology," 2019 10th International Conference on Computing, Communication and Networking Technologies (ICCCNT), Kanpur, India, 2019, pp. 1-5,

- [18] A. Awny et al., "A Linear Differential Transimpedance Amplifier for 100-Gb/s Integrated Coherent Optical Fiber Receivers," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 66, no. 2, pp. 973-986, Feb. 2018

- [19] R. Nagulapalli, K. Hayatleh, S. Barker, B. N. K. Reddy and B. Seetharamulu, "A High Frequency CMRR improvement technique for Differential Amplifiers in 45nm CMOS," 2019 10th International Conference on Computing, Communication and Networking Technologies (ICCCNT), Kanpur, India, 2019, pp. 1-5

- [20] M. Kroh et al., "Monolithic Photonic-Electronic Linear Direct Detection Receiver for 56Gbps OOK," ECOC 2016; 42nd European

- Conference on Optical Communication, Dusseldorf, Germany, 2016, pp. 1-3.

- [21] R. Nagulapalli, K. Hayatleh, S. Barker, S. Zourob, A. Venkatareddy, "A CMOS technology friendly wider bandwidth opamp frequency compensation", *Electrical Computer and Communication Technologies (ICECCT) 2017 Second International Conference on*, pp. 1-4, 2017.

- [22] Nagulapalli R., Hayatleh K., Barker S., Zourob S., Yassine N., Naresh Kumar Reddy B. (2019) A 31 ppm/oC Pure CMOS Bandgap Reference by Exploiting Beta-Multiplier. In: Rajaram S., Balamurugan N., Gracia Nirmala Rani D., Singh V. (eds) VLSI Design and Test. VDAT 2018. Communications in Computer and Information Science, vol 892. Springer, Singapore

- [23] W.M. Sansen, Analog Design Essentials, Springer-Verlag, 2006, ISBN 978-0-387-25746-4.