## A Low Noise Amplifier Suitable for Biomedical Recording Analog Front-End in 65nm CMOS Technology

## R. Nagulapalli, K. Hayatleh, S. Barker, A.A. Tammam, N. Yassine, B. Yassine, M. Ben-Esmael.

Abstract: This paper presents a fully integrated Front-end, low noise amplifier, dedicated to the processing of various types of bio-medical signals, such as Electrocardiogram (ECG), Electroencephalography (EEG), Axon Action Potential (AAP). A novel noise reduction technique, for an operational transconductance amplifier (OTA), has been proposed. This adds a current steering branch parallel to the differential pair, with a view to reducing the noise contribution by the cascode current sources. Hence, this reduces the overall input referred noise of the Low Noise Amplifier (LNA), without adding any additional power. The proposed technique implemented in 65nm CMOS technology achieves 30dB closed loop voltage gain, 0.05Hz lower cut-off frequency and 100MHz 3-dB bandwidth. It operates at 1.2V power supply and draws 1µA static current. The prototype described in this paper occupies 3300µm<sup>2</sup> silicon area.

## Key Words: ECG, EEG, AAP, VT, VF.

**1. Introduction:** The number of deaths, because of cardiac arrhythmia, totals around 4 million worldwide [1]. The arrhythmias of ventricular origins, ventricular tachycardia (VT) or ventricular fibrillation (VF) are the leading causes of death by cardiac arrhythmia. Ventricular arrhythmia is an abnormal ECG rhythm and is responsible for 75%–85% of deaths in patients with heart disease. Most ventricular arrhythmias are caused by coronary heart disease, hypertension and cardiomyopathy, which lead to death if it not treated or diagnosed at an early stage [1]. VT is a fast rhythm of three or more, consecutive beats originating from the ventricles at a rate higher than 100 beats/min. VF is a severely abnormal heart rhythm, due to the lower heart chambers contracting in an unsynchronized manner. This results in having little or no blood pumped through the heart, leading to life-threatening health conditions [2].

Electrodes are used to sense ECG signals for processing it in the electrical domain. The ECG signal consist mainly of three components, actual differential ECG signal, the offset voltage introduced by the electrodes and common-mode interference from 50/60Hz power supply. The actual differential ECG signal that appears between the electrodes in any lead configuration is limited to 0.1-5 mV in magnitude and 0.05 Hz to 150 Hz in frequency. The magnitude of this ECG signal, coupled with the resolution required from the ECG signal, determines the dynamic range for the front-end. The frequency content of this signal determines the bandwidth of the analog front-end. The skin-electrode interface provides an additional DC offset of 300 mV which needs to be compensated so that the signal chain is not saturated. Additionally, the human body can pick up large interference signals from the power lines, fluorescent lights, and so forth. This interference can be manifest as either a normal-mode signal or a common-mode signal. The normal-mode interference can be mitigated by software, implemented with a 50-Hz/60-Hz notch filter.

The paper contains five sections. Section-I is the introduction. Section-II and Section-III are the LNA design challenges and existing techniques. Section-IV is the proposed split differential pair technique. section-V contains a summary of the simulation results of the prototype. Finally, section-VI summarises and concludes the paper.

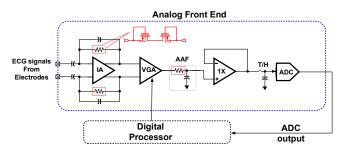

2. ECG Analog Front-End requirements: ECG signals pose several challenges to the hardware. Mainly, the input referred noise of the transceiver should be of order of 10µV, to meet the stringent sensitivity requirements. To allow the device to be a wearable option, the transceiver should consume as little amount of power possible, using a low voltage power supply. Multi-electrode sensing is often desirable for this purpose. However, the problem with the multi-electrode system is cross-talk induced noise (common-mode noise) due to the interaction among the electrodes. Hence, a very high common mode rejection ratio (CMRR) is required. There have been several attempts to develop hardware for accurate ECG analysis and hardware and classification [3]. Fig. 1 shows the multi-electrode neural recording system. Electrodes are used to convert the biological signals into electrical signals and these signals are fed to the electrical part of the recording system. These electrical signals are large DC offset voltages that are mainly due to leakage of DC current (100pA) and a high impedance at the interface. To summarise, the challenges of the front-end low-noise amplifier design are low noise, high

gain, low form-factor while consuming a minimal power. This paper considers the reduction of the input-referred noise without increasing the power supply voltage.

Fig. 1. ECG Analog Front-End block diagram [2].

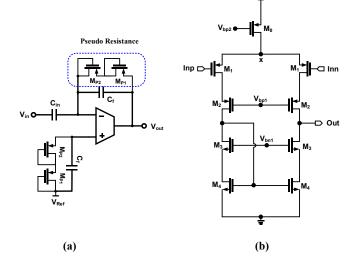

3. Low Noise Amplifier (LNA): The low noise amplifier (LNA) is a high gain amplifier required for the frontend instrumentation amplifier (IA). LNA uses a capacitive feedback amplifier to amplify the signal while rejecting the DC offset from the electrodes. Fig. 2 (a) shows the amplifier feedback capacitor  $C_F$  and the input capacitor  $C_{IN}$ , where  $M_{P2}$ ,  $M_{P1}$  form the feedback resistance. This defines the DC operating point by enabling the feedback in the low-frequency range, which we determined in our previous work [4]. The closed loop voltage gain is given by the ratio  $C_{IN}$  /  $C_F$ .

Fig. 2. (a) Closed loop LNA (b) Telescopic Cascode OTA (biasing not shown)

The input-referred noise of the LNA is contributed by the feedback resistors and OTA. The noise of the feedback resistor can be neglected due to low bandwidth. The overall noise of the LNA is mostly contributed by the OTA. Telescopic and folded cascode OTAs are the typical choices in LNAs, due to their high gain and simple dominate pole compensation nature. Since folded-cascode OTA generally use more current mirrors, discussed in our previous work [4], it's input referred offset is high due to random device mismatch. Therefore, a telescopic cascode is presented in this paper despite the fact the maximum voltage swing is less, in comparsion with the folded cascode OTA. Fig. 2(b) shows the telescopic cascode OTA, where  $M_1,M_{1a}$  forms the differential pair, while  $M_2,M_3,M_4$  comprise the current sources. The general expression for the Telescopic cascode voltage gain is given as follows [5]:

$$\frac{g_{m1}}{\frac{g_{ds1}g_{ds2}}{g_{m1}} + \frac{g_{ds3}g_{ds4}}{g_{m4}}} \tag{1}$$

Input-referred noise is dominated by the differential pair transistors  $M_1$  and the load PMOS current source  $M_4$ . Cascode transistors  $M_2$  and  $M_3$  have little contributie since their sources are connected to another transistor drain, so that  $g_{m2},g_{m3}$  will be decreased. Hence, there is negligible noise contribution. The spectral density of the thermal noise is given by [10]:

$$V_{n,thermal}^2 = 8KT \tau \frac{1}{g_{m1}} \left( 1 + \frac{g_{m2}}{g_{m1}} \right) \Delta \mathbf{f}$$

(2a)

$$V_{Flicker}^{2} = 2 \left[ \frac{K_{P}}{C_{OX}W_{1}L_{1}} + \frac{K_{N}}{C_{OX}W_{2}L_{2}} \left( \frac{g_{m2}}{g_{m1}} \right)^{2} \right] \frac{\Delta f}{f}$$

(2b)

where K is the Boltzmann Constant, T is the temperature in Kelvin,  $\tau$  is the thermal noise coefficient which is ~2/3 for older CMOS technologies and >1 for sub micron technologies.

The input referred rms noise is calculated by the integrating of the above result within the intersted frequency band. As a result of increasing  $g_{m1}$  the noise will decrease additionally the contribution from the differential pair and current source will be reduced.  $g_{m1}$  can be increased either by increasing the bias current or by increasing the device size. The increase of the bias current will decrease the noise contribution of M1, while at the same time, it increases the contribution of M4. Prominent in older CMOS technologies,  $g_m$  increases with current lieanrly [5]. In the modern deep sub-micron technologies (from 65nm CMOS), the transistor  $g_m$  can be expressed as followin:

$$g_m = \frac{1}{2} \mu_n C_{ox} W E_{sat} \tag{3}$$

where  $C_{ox}$  is the oxide capacitance,  $\mu_n$  is the carrier mobility, W is the width of the transistor and  $E_{sat}$  is the carrier velocity satuartion electric field.

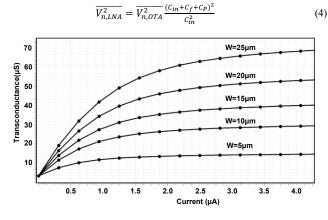

From equation (3) gm increases linearly with current, for a low current range. gm is almost independent of current (for the first order) and can only be increased by increasing the width. Fig. 3 shows the variations of gm with changing values of current and width. The results show a small increase of  $g_m$  from 12µS to 14µS when doubling the current from 2µA to  $4\mu A$  in a 5µm wide device. Whereas, increasing the width from 5µm to 10µm doubles gm. Hence, current has less significant impact on the noise performance. In contrast the increase of the width will have significant improvement on the noise performance. Hence, it will increase the input paracitic capaciatnce (CP) of the OTA. The increase of Cp will have the following impact on the transceiver performance. The input signal of the LNA will experience a potential division due to the Cin and C<sub>p</sub>, thus limiting the available signal to LNA. Due to the weak nature of the bio-medical signal, a large value of Cp will effect the signal to noise ratio of the tranceiver. The noise of the OTA will appear at the LNA input with a multiplication factor given by equation (4), which shows that a large value of CP will increase the overal noise. The feedback factor of the LNA will decrease as result of large value of C<sub>p</sub>[4].

Fig. 3. Telescopic Opamp Transconuctance Characteristics

It should be noted that increasing the input device size, with a view to minimise the noise, would not be effective method to decrease the noise. Several reserchers have proposed different methods to decrease noise [6-9], where the reduction in noise achieved was dependent on the technology and/or design optimization.

gm/id methodology has been used to optimise the current mirror and differential pair transistors noise contribution [6]. The degenerated folded cascode LNA, provides the stacking inverter based LNA that is efficient but it inherits poor linearity [7-8]. There is a need for a special technique to reduce the noise of any architecture. This paper presents a novel technique to reduce the noise.

4. Proposed Low Noise Solution: The fundamental idea behind the proposal is as follows. In equation 2(b),  $g_{m1}$  should be maximized and  $g_{m2}$  shoud be minimized in order to minimze the noise. In the conventional telesecopic cascode, the differential pair and cascode devices carries the same current. By modulating the bias current, both  $g_m$ 's change in the same direction, controry to the requirement. low noise is achieved at the output by providing a different bias current for the differential pair (M<sub>1</sub>) and the cascode current source (M<sub>4</sub>).

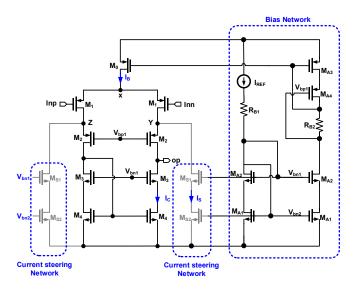

Fig. 4. Telescopic OTA with reduced input-reffered noise

Fig. 4 shows the proposed technique which allows us to pull current out of the differential pair, in order to reduce the bias current in M<sub>4</sub> (the current source). Hence, this reduces the noise without compromising the cureent in M<sub>1</sub>. A standard cascode bias network, consisting of M<sub>A1</sub>, M<sub>A2</sub>, M<sub>A3</sub>, M<sub>A4</sub>, R<sub>B1</sub>, R<sub>B2</sub>, has been used to simplify the bias complications [5]. Generally, the differential pair current (I<sub>B</sub>/2) will be set by the unity gain bandwidth (UGB) requirements or noise contribution. M<sub>4</sub> current is (I<sub>B</sub>/2 – I<sub>S</sub>) minimized by adjusting the steering current (I<sub>S</sub>). Therefore, this minimizes the contribution of M<sub>4</sub>. M<sub>S1</sub> and M<sub>S2</sub> form the cascode current steering device. While M<sub>S2</sub> contributes additional noise, it can be optimized, by reducing additional noise, without affecting any other parameters of the opamp. This is achieved by using it as a current source. The transconductance of the devices can be expressed as:

$$g_{m1} = \sqrt{u_n c_{ox} I_B \left(\frac{W}{L}\right)_1} \quad g_{m4} = \sqrt{2u_n c_{ox} \left(\frac{I_B}{2} - I_S\right) \left(\frac{W}{L}\right)_4} \tag{5}$$

$$g_{mS2} = \sqrt{2u_n c_{ox} I_S \left(\frac{W}{L}\right)_{S2}} \tag{6}$$

The overal input-referred noise, including  $M_{\rm S2}$ , can be expressed by substituing the expressions above into the equation below:

$$V_{in}^2 = 8KT \tau \frac{1}{g_{m1}} \left( 1 + \frac{g_{m4}}{g_{m1}} + \frac{g_{m52}}{g_{m1}} \right)$$

(7)

$$V_{in}^{2} = \frac{4\kappa T_{\rm Y}}{\sqrt{u_{n}c_{ox}I_{B}\left(\frac{W}{L}\right)_{1}}} \left(1 + \sqrt{\frac{I_{B} - 2I_{S}\left(\frac{W}{L}\right)_{4}}{I_{B}} + \sqrt{\frac{2I_{S}\left(\frac{W}{L}\right)_{S2}}{I_{B}}\left(\frac{W}{L}\right)_{1}}}\right)$$

(8)

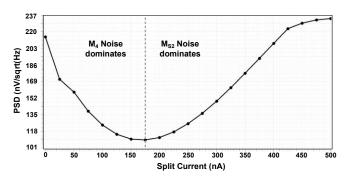

Equation 8 shows a trade off between the noise contribution of  $M_4$  and  $M_{s2}$ , but since the steering current is low, the  $M_{s2}$  noise contribution is low, while the  $M_4$  noise contribution is high. Similiarly, when the split current is high,  $M_{s2}$  noise contribution is high, while  $M_4$  noise contribution is low. Hence, there will be an optimal steering current which can be expressed by finding the derivative of equation (5). However, this will be very complicated and less intuitive to implement and it may not be correct due to submicron technology noise factor x and full noise equations being unknown. Hence, we designed an amplifier with 1µA bias current through  $M_0$  and swept the steering current. Fig. 5 shows the low frequency noise spectal density versus split current. This paper covers thermal noise, but omits reviewing flicker noise, thereby minimizing the complication. The proposed design in this paper

minimises both noise types. Theoretically, the input referred noise, due to the split current (I<sub>S</sub>), will decrease because  $M_4$  contributes low noise when split current is high (mentioned above). Note this trend continues towards 0.175 $\mu$ A. Furthermore, the current above 0.175 $\mu$ A will lead to an overall input referred noise, that increases with current I<sub>s</sub>. This is due to the increase in the  $M_{S2}$  noise (Fig. 4) which dominates the decrease in the  $M_4$  noise. It should be noted that the optimal I<sub>s</sub> value depends on the technology parameters. Additionally, current I<sub>s</sub> has a direct effect on the open loop gain of the OTA. This is due to the small signal current of transitor  $M_1$  experiencing a divison at node Y. A small current will flow into  $M_2$  and  $M_{s1}$ . Hence, the signal current flow into the output will be slightly reduced, as well as the gain. For the usual case, the impedance of  $M_2$  is  $I_3 m_2$ , which leads to a reduction in the gain.

Fig. 5. Telescopic OTA with reduced input-reffered noise

The effective small signal gm can be expressed as  $g_{m1} \frac{g_{m2}}{g_{m2} + \frac{g_{dss1}g_{dss2}}{g_{m3}}}$ because M<sub>1</sub> signal current will be divided into two components, at node Y. Effective cascode conductance at the output node can be derived as  $\frac{g_{ds3}g_{ds3}}{g_{m3}} + \frac{g_{ds2}g_{ds1}}{g_{m2}}$ . Hence, by using effective transconductance and output conductance, the voltage gain can be expressed as follows.

$$Gain = \frac{g_{m1} \frac{g_{m2}}{g_{m2} + \frac{g_{dss1}g_{dss2}}{g_{m3}}}}{\frac{g_{ds3}g_{ds4}}{g_{m3}} + \frac{g_{ds2}g_{ds1}}{g_{m2}}}$$

(9)

Since the split current is very high,  $M_{s2}$  carries a larger current than  $M_2$ . This will reduce the impedance of the split current source ( $M_{s2}$ ) and the gain will be derived from conventional means. To reduce the effect of Is on the voltage gain, the impedance of the current steering network should be very high, hence the signal current flowing into current steering network is much less. To reduce this effect, the current steering network, with the cascode current source, is formed by  $M_{s1}$ , $M_{s2}$ , rather than with  $M_{s2}$  only.

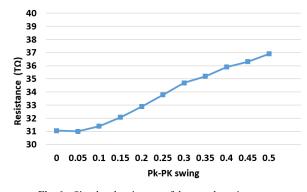

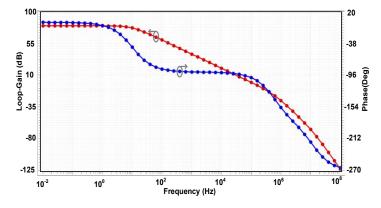

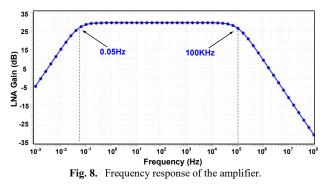

5. Implementaion Details: To demonstarte the proposed noise reduction technique, the LNA Front-end has been implemented in 65nm CMOS TSMC technology. The circuit design functions at 1.2V power supply voltage and draws  $1\mu A$  current at room temperature. The aim is to achieve a LNA voltage Gain of 30dB, with selected capactiors Cin,Cf having capacitances of 3pF and 0.1pF respectively. To achieve an upper cut-off frequency ~0.05Hz, the feedback Pseudo resistance formed by  $M_{P2}$  and  $M_{P1}$  should be larger than  $30T\Omega$ . Figure 6 shows the resistance variation versus the voltage swing across the pseudo resistance. The transistors sizes of M<sub>p2</sub> and M<sub>p1</sub> are selected so that the resistance values are larger than that of the required, with a view to make the cut-off frequency less than 0.05Hz. The open loop gain of the OTA is 82dB, which is sufficient to give 0.01% accuracy and the phase margin is  $72^{\circ}$ , which indicates very stable closed loop operation, fig. 7 shows the frequency response of the opamp. Fig. 8 shows the simulated closed loop gain of the LNA. The simulated results show the mid-band gain is equal to 30dB, the lower cut-off frequency equal to ~0.05Hz and the upper cutoff frequency equal to 100KHz, to process high frequency biodemedical signals (see Figure 7). The upper cut-off frequency depends on the ratio of the input differential pair of the  $g_m$  and the load capacitance (the input capacitance of the VGA)[10].

Fig. 6. Simulated resistance of the pseudo resistance.

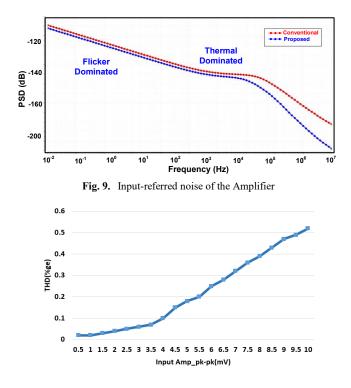

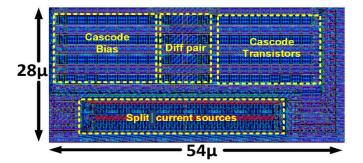

Fig. 9 shows the simulated input referred noise power spectral density (PSD) of the proposed and conventional cascade opamp. As described in the section 3, setting the value for the split current to 0.175µA achieves optimal noise performance. The PSD of the proposed design is 3dB lower than the cascade opamp, across the frequency band of interest. The flicker noise corner frequency is 35 KHz, the integrated RMS noise is ~  $9.85\mu$ V for the cascade opamp, whereas for the proposed design, it is 6.9  $\mu$ V, which is 30% better. Due to the weak amplitude of the signal, the LNA needs a high linearity to process, hence reducing the power supply and the common mode coupling. The total harmonic distortion (THD) has been simulated by varying the input signal amplitude with the maximum value of 4mV of the input amplitude. The THD was below 0.1%, but beyond 4mV amplitude and degraded rapidly. This was due to the OTA transistors experiencing a significant percentage of the signal swing compared to the operating point. A very reasonable 0.5% of the THD would process most signals [6]. Fig. 10 shows the simulated THD versus input amplitude. Figure 11 shows the layout of the proposed LNA, which occupies 1512µm<sup>2</sup> active silicon area.

Fig. 10. THD versus applied input amplitude.

Fig. 11. Layout of the proposed circuit.

**6.** Conclusion: This paper presents a technique to reduce the input referred noise of the OTA by decreasing the Cascode current source gm, without increasing the power dissipation. A current splitting branch will reduce the Cascode devices current for any given bias current. The implementation in 65nm and post layout simulations, with Spectre simulator, shows that 30% noise reduction and 30dB voltage gain. The LNA draws  $1\mu$ A current from 1.2V power supply.

R. Nagulapalli, K. Hayatleh, S. Barker, A.A. Tammam, N. Yassine, B. Yassine, M. Ben-Esmael.

(Faculty of Technology, Design and Environment, Oxford Brookes University, Wheatley Campus, Oxford, OX33 1HX, UK) E-mail: khayatleh@brookes.ac.uk

The authors acknowledge and would like to thank Dr Bryan Hart for his valuable time and advice on the writing of this paper.

## References

1. J. W. Schleifer and K. Srivathsan, "Ventricular arrhythmias: State of the art," Cardiol. Clin., vol. 31, no. 4, pp. 595–605, 2013

2. C. J. Garratt, Mechanisms and Management of Cardiac Arrhythmias. London, U.K.: BMJ Books, 2001.

3. Yen-Po Chen, Dongsuk Jeon, Yoonmyung Lee, Yejoong Kim, Zhiyoong Foo, Inhee Lee, Nicholas B. Langhals, Grant Kruger, Hakan Oral, Omer Berenfeld, Zhengya Zhang, David Blaauw, Dennis Sylvester, "An Injectable 64 nW ECG Mixed-Signal SoC in 65 nm for Arrhythmia Monitoring", *Solid-State Circuits IEEE Journal of*, vol. 50, pp. 375-390, 2015, ISSN 0018-9200.

4. Nagulapalli, R., Hayatleh, K., Barker, S. et al. Analog Integr Circ Sig Process (2018). https://doi.org/10.1007/s10470-018-1148-y

5. Behzad Razavi, Design of Analog CMOS Integrated Circuits, New Work: McGraw-Hill, 2001.

6. R. R. Harrison and C. Charles, "A low-power low-noise CMOS amplifier for neural recording applications," Solid-State Circuits, IEEE Journal of, vol. 38, pp. 958-965, 2003.

7. W. Wattanapanitch, M. Fee, R. Sarpeshkar, "An energy-efficient micropower neural recording amplifier", *IEEE Trans. Biomed. Circuits Syst.*, vol. 1, no. 2, pp. 136-147, 2007.

8. S. Song et al., "A low-voltage chopper-stabilized amplifier for fetal ECG monitoring with a 1.41 power efficiency factor", *IEEE Trans. Biomed. Circuits Syst.*, vol. 9, no. 2, pp. 237-247, Apr. 2015.

9. B. Johnson, A. Molnar, "An orthogonal current-reuse amplifier for multi-channel sensing", *IEEE J. Solid-State Circuits*, vol. 48, no. 6, pp. 1487-1496, Jun. 2013.

10. T.H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, Cambridge University Press, United Kingdom, 1998.